## **Programmable Controller**

## QCPU User's Manual (Multiple CPU System)

-Q00CPU -Q01CPU -Q02(H)CPU -Q06HCPU -Q12HCPU -Q25HCPU -Q02PHCPU -Q06PHCPU -Q12PHCPU -Q25PHCPU -Q00UCPU -Q01UCPU -Q02UCPU -Q03UD(E)CPU -Q03UDVCPU -Q04UD(E)HCPU -Q04UDVCPU -Q04UDPVCPU -Q06UD(E)HCPU -Q06UDVCPU -Q06UDPVCPU -Q10UD(E)HCPU -Q13UD(E)HCPU -Q13UDVCPU -Q13UDPVCPU -Q20UD(E)HCPU -Q26UD(E)HCPU -Q26UDVCPU -Q26UDPVCPU -Q50UDEHCPU -Q100UDEHCPU

## SAFETY PRECAUTIONS

(Read these precautions before using this product.)

Before using this product, please read this manual and the relevant manuals carefully and pay full attention to safety to handle the product correctly.

In this manual, the safety precautions are classified into two levels: " A WARNING" and " CAUTION".

Under some circumstances, failure to observe the precautions given under "<u>CAUTION</u>" may lead to serious consequences.

Observe the precautions of both levels because they are important for personal and system safety. Make sure that the end users read this manual and then keep the manual in a safe place for future reference.

### [Design Precautions]

##

- Configure safety circuits external to the programmable controller to ensure that the entire system operates safely even when a fault occurs in the external power supply or the programmable controller.

Failure to do so may result in an accident due to an incorrect output or malfunction.

- (1) Configure external safety circuits, such as an emergency stop circuit, protection circuit, and protective interlock circuit for forward/reverse operation or upper/lower limit positioning.

- (2) The programmable controller stops its operation upon detection of the following status, and the output status of the system will be as shown below.

|                                                                                                 | Q series module                                                        | AnS/A series module        |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------|

| Overcurrent or overvoltage protection of the power supply module is activated.                  | All outputs are turned off                                             | All outputs are turned off |

| The CPU module detects an error such as a watchdog timer error by the self-diagnostic function. | All outputs are held or turned off according to the parameter setting. | All outputs are turned off |

All outputs may turn on when an error occurs in the part, such as I/O control part, where the programmable controller CPU cannot detect any error. To ensure safety operation in such a case, provide a safety mechanism or a fail-safe circuit external to the programmable controller. For a fail-safe circuit example, refer to the QCPU User's Manual (Hardware Design, Maintenance and Inspection).

(3) Outputs may remain on or off due to a failure of an output module relay or transistor. Configure an external circuit for monitoring output signals that could cause a serious accident.

## [Design Precautions]

##

- In an output module, when a load current exceeding the rated current or an overcurrent caused by a load short-circuit flows for a long time, it may cause smoke and fire. To prevent this, configure an external safety circuit, such as a fuse.

- Configure a circuit so that the programmable controller is turned on first and then the external power supply. If the external power supply is turned on first, an accident may occur due to an incorrect output or malfunction.

- For the operating status of each station after a communication failure, refer to manuals relevant to the network. Incorrect output or malfunction due to a communication failure may result in an accident.

- When connecting a peripheral with the CPU module or connecting an external device, such as a personal computer, with an intelligent function module to modify data of a running programmable controller, configure an interlock circuit in the program to ensure that the entire system will always operate safely. For other forms of control (such as program modification or operating status change) of a running programmable controller, read the relevant manuals carefully and ensure that the operation is safe before proceeding. Especially, when a remote programmable controller is controlled by an external device, immediate action cannot be taken if a problem occurs in the programmable controller due to a communication failure. To prevent this, configure an interlock circuit in the sequence program, and determine corrective actions to be taken between the external device and CPU module in case of a communication failure.

### [Design Precautions]

- Do not install the control lines or communication cables together with the main circuit lines or power cables. Keep a distance of 100mm (3.94 inches) or more between them. Failure to do so may result in malfunction due to noise.

- When a device such as a lamp, heater, or solenoid valve is controlled through an output module, a large current (approximately ten times greater than normal) may flow when the output is turned from off to on. Take measures such as replacing the module with one having a sufficient current rating.

- After the CPU module is powered on or is reset, the time taken to enter the RUN status varies depending on the system configuration, parameter settings, and/or program size. Design circuits so that the entire system will always operate safely, regardless of the time.

## [Installation Precautions]

##

- Use the programmable controller in an environment that meets the general specifications in the QCPU User's Manual (Hardware Design, Maintenance and Inspection). Failure to do so may result in electric shock, fire, malfunction, or damage to or deterioration of the product.

- To mount the module, while pressing the module mounting lever located in the lower part of the module, fully insert the module fixing projection(s) into the hole(s) in the base unit and press the module until it snaps into place. Incorrect mounting may cause malfunction, failure or drop of the module. When using the programmable controller in an environment of frequent vibrations, fix the module with a screw. Tighten the screw within the specified torque range. Undertightening can cause drop of the screw, short circuit, or malfunction. Overtightening can damage the screw and/or module, resulting in drop, short circuit, or malfunction.

- When using an extension cable, connect it to the extension cable connector of the base unit securely. Check the connection for looseness. Poor contact may cause incorrect input or output.

- When using a memory card, fully insert it into the memory card slot. Check that it is inserted completely. Poor contact may cause malfunction.

- When using an SD memory card, fully insert it into the SD memory card slot. Check that it is inserted completely. Poor contact may cause malfunction.

- Securely insert an extended SRAM cassette into the cassette connector of a CPU module. After insertion, close the cassette cover to prevent the cassette from coming off. Poor contact may cause malfunction.

- Shut off the external power supply (all phases) used in the system before mounting or removing the module. Failure to do so may result in damage to the product. A module can be replaced online (while power is on) on any MELSECNET/H remote I/O station or in the system where a CPU module supporting the online module change function is used. Note that there are restrictions on the modules that can be replaced online, and each module has its predetermined replacement procedure. For details, refer to the relevant sections in the QCPU User's Manual (Hardware Design, Maintenance and Inspection) and in the manual for the corresponding module.

- Do not directly touch any conductive parts and electronic components of the module, memory card, SD memory card, or extended SRAM cassette. Doing so can cause malfunction or failure of the module.

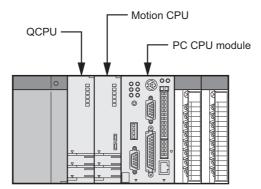

- When using a Motion CPU module and modules designed for motion control, check that the combinations of these modules are correct before applying power. The modules may be damaged if the combination is incorrect. For details, refer to the user's manual for the Motion CPU module.

## [Wiring Precautions]

- Shut off the external power supply (all phases) used in the system before wiring. Failure to do so may result in electric shock or damage to the product.

- After installation and wiring, attach the included terminal cover to the module before turning it on for operation. Failure to do so may result in electric shock.

## [Wiring Precautions]

- Individually ground the FG and LG terminals of the programmable controller with a ground resistance of 100Ω or less. Failure to do so may result in electric shock or malfunction.

- Use applicable solderless terminals and tighten them within the specified torque range. If any spade solderless terminal is used, it may be disconnected when the terminal screw comes loose, resulting in failure.

- Check the rated voltage and terminal layout before wiring to the module, and connect the cables correctly. Connecting a power supply with a different voltage rating or incorrect wiring may cause a fire or failure.

- Connectors for external devices must be crimped or pressed with the tool specified by the manufacturer, or must be correctly soldered. Incomplete connections may cause short circuit, fire, or malfunction.

- Securely connect the connector to the module. Poor contact may cause malfunction.

- Do not install the control lines or communication cables together with the main circuit lines or power cables. Keep a distance of 100mm (3.94 inches) or more between them. Failure to do so may result in malfunction due to noise.

- Place the cables in a duct or clamp them. If not, dangling cable may swing or inadvertently be pulled, resulting in damage to the module or cables or malfunction due to poor connection.

- Check the interface type and correctly connect the cable. Incorrect wiring (connecting the cable to an incorrect interface) may cause failure of the module and external device.

- Tighten the terminal screws within the specified torque range. Undertightening can cause short circuit, fire, or malfunction. Overtightening can damage the screw and/or module, resulting in drop, short circuit, or malfunction.

- Prevent foreign matter such as dust or wire chips from entering the module. Such foreign matter can cause a fire, failure, or malfunction.

- A protective film is attached to the top of the module to prevent foreign matter, such as wire chips, from entering the module during wiring. Do not remove the film during wiring. Remove it for heat dissipation before system operation.

- When disconnecting the cable from the module, do not pull the cable by the cable part. For the cable with connector, hold the connector part of the cable. For the cable connected to the terminal block, loosen the terminal screw. Pulling the cable connected to the module may result in malfunction or damage to the module or cable.

- Mitsubishi programmable controllers must be installed in control panels. Connect the main power supply to the power supply module in the control panel through a relay terminal block. Wiring and replacement of a power supply module must be performed by qualified maintenance personnel with knowledge of protection against electric shock. For wiring methods, refer to the QCPU User's Manual (Hardware Design, Maintenance and Inspection).

### [Startup and Maintenance Precautions]

## 🔥 WARNING

- Do not touch any terminal while power is on. Doing so will cause electric shock or malfunction.

- Correctly connect the battery connector. Do not charge, disassemble, heat, short-circuit, solder, or throw the battery into the fire. Also, do not expose it to liquid or strong shock. Doing so will cause the battery to produce heat, explode, ignite, or leak, resulting in injury and fire.

- Shut off the external power supply (all phases) used in the system before cleaning the module or retightening the terminal screws, connector screws, or module fixing screws. Failure to do so may result in electric shock or cause the module to fail or malfunction.

### [Startup and Maintenance Precautions]

- Before performing online operations (especially, program modification, forced output, and operating status change) for the running CPU module from the peripheral device connected, read relevant manuals carefully and ensure the safety. Improper operation may damage machines or cause accidents.

- Do not disassemble or modify the modules. Doing so may cause failure, malfunction, injury, or a fire.

- Use any radio communication device such as a cellular phone or PHS (Personal Handy-phone System) more than 25cm (9.85 inches) away in all directions from the programmable controller.

Failure to do so may cause malfunction.

- Shut off the external power supply (all phases) used in the system before mounting or removing the module. Failure to do so may cause the module to fail or malfunction. A module can be replaced online (while power is on) on any MELSECNET/H remote I/O station or in the system where a CPU module supporting the online module change function is used. Note that there are restrictions on the modules that can be replaced online, and each module has its predetermined replacement procedure. For details, refer to the relevant sections in the QCPU User's Manual (Hardware Design, Maintenance and Inspection) and in the manual for the corresponding module.

- After the first use of the product, do not mount/remove the module to/from the base unit, and the terminal block to/from the module, and do not insert/remove the extended SRAM cassette to/from the CPU module more than 50 times (IEC 61131-2 compliant) respectively. Exceeding the limit of 50 times may cause malfunction.

- After the first use of the product, do not insert/remove the SD memory card to/from the CPU module more than 500 times. Exceeding the limit may cause malfunction.

- Do not drop or apply shock to the battery to be installed in the module. Doing so may damage the battery, causing the battery fluid to leak inside the battery. If the battery is dropped or any shock is applied to it, dispose of it without using.

- Before handling the module, touch a grounded metal object to discharge the static electricity from the human body. Failure to do so may cause the module to fail or malfunction.

## [Disposal Precautions]

##

When disposing of this product, treat it as industrial waste. When disposing of batteries, separate them from other wastes according to the local regulations. (For the Battery Directive in EU member states, refer to the QCPU User's Manual (Hardware Design, Maintenance and Inspection).)

### [Transportation Precautions]

##

• When transporting lithium batteries, follow the transportation regulations. (For details of the regulated models, refer to the QCPU User's Manual (Hardware Design, Maintenance and Inspection).)

## **CONDITIONS OF USE FOR THE PRODUCT**

(1) Mitsubishi programmable controller ("the PRODUCT") shall be used in conditions;

i) where any problem, fault or failure occurring in the PRODUCT, if any, shall not lead to any major or serious accident; and

ii) where the backup and fail-safe function are systematically or automatically provided outside of the PRODUCT for the case of any problem, fault or failure occurring in the PRODUCT.

(2) The PRODUCT has been designed and manufactured for the purpose of being used in general industries.

MITSUBISHI SHALL HAVE NO RESPONSIBILITY OR LIABILITY (INCLUDING, BUT NOT LIMITED TO ANY AND ALL RESPONSIBILITY OR LIABILITY BASED ON CONTRACT, WARRANTY, TORT, PRODUCT LIABILITY) FOR ANY INJURY OR DEATH TO PERSONS OR LOSS OR DAMAGE TO PROPERTY CAUSED BY the PRODUCT THAT ARE OPERATED OR USED IN APPLICATION NOT INTENDED OR EXCLUDED BY INSTRUCTIONS, PRECAUTIONS, OR WARNING CONTAINED IN MITSUBISHI'S USER, INSTRUCTION AND/OR SAFETY MANUALS, TECHNICAL BULLETINS AND GUIDELINES FOR the PRODUCT. ("Prohibited Application")

Prohibited Applications include, but not limited to, the use of the PRODUCT in;

- Nuclear Power Plants and any other power plants operated by Power companies, and/or any

other cases in which the public could be affected if any problem or fault occurs in the PRODUCT.

- Railway companies or Public service purposes, and/or any other cases in which establishment of a special quality assurance system is required by the Purchaser or End User.

- Aircraft or Aerospace, Medical applications, Train equipment, transport equipment such as Elevator and Escalator, Incineration and Fuel devices, Vehicles, Manned transportation, Equipment for Recreation and Amusement, and Safety devices, handling of Nuclear or Hazardous Materials or Chemicals, Mining and Drilling, and/or other applications where there is a significant risk of injury to the public or property.

Notwithstanding the above, restrictions Mitsubishi may in its sole discretion, authorize use of the PRODUCT in one or more of the Prohibited Applications, provided that the usage of the PRODUCT is limited only for the specific applications agreed to by Mitsubishi and provided further that no special quality assurance or fail-safe, redundant or other safety features which exceed the general specifications of the PRODUCTs are required. For details, please contact the Mitsubishi representative in your region.

## **INTRODUCTION**

This manual describes the system configurations, functions, and communication methods with external devices required in a multiple CPU system.

Before using this product, please read this manual and the relevant manuals carefully and develop familiarity with the functions and performance of the Q series programmable controller to handle the product correctly. When applying the program examples introduced in this manual to the actual system, ensure the applicability and confirm that it will not cause system control problems.

■Relevant CPU modules:

| CPU module                  | Model                                                                                                                                                                                                                                                                  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Basic model QCPU            | Q00CPU, Q01CPU                                                                                                                                                                                                                                                         |

| High Performance model QCPU | Q02(H)CPU, Q06HCPU, Q12HCPU, Q25HCPU                                                                                                                                                                                                                                   |

| Process CPU                 | Q02PHCPU, Q06PHCPU, Q12PHCPU, Q25PHCPU                                                                                                                                                                                                                                 |

| Universal model QCPU        | Q00UCPU, Q01UCPU, Q02UCPU, Q03UD(E)CPU, Q03UDVCPU,<br>Q04UD(E)HCPU, Q04UDVCPU, Q04UDPVCPU, Q06UD(E)HCPU,<br>Q06UDVCPU, Q06UDPVCPU, Q10UD(E)HCPU, Q13UD(E)HCPU,<br>Q13UDVCPU, Q13UDPVCPU, Q20UD(E)HCPU, Q26UD(E)HCPU,<br>Q26UDVCPU, Q26UDPVCPU, Q50UDEHCPU, Q100UDEHCPU |

Remark

• This manual does not describe the specifications and precautions of the power supply modules, base units, extension cables, memory cards, SD memory cards, extended SRAM cassettes, and batteries as well as the peripheral configurations.

QCPU User's Manual (Hardware Design, Maintenance and Inspection)

• For the functions of CPU modules when used in a system other than a multiple CPU system, refer to the following. User's Manual (Function Explanation, Program Fundamentals) for the CPU module used . . . . . . . . . .

## Memo

| SAFETY PRECAUTIONS                | . 1 |

|-----------------------------------|-----|

| CONDITIONS OF USE FOR THE PRODUCT | . 7 |

| INTRODUCTION                      | . 8 |

| MANUALS                           | 12  |

| MANUAL PAGE ORGANIZATION          | 14  |

| TERMS                             | 15  |

|                                   |     |

#### CHAPTER 1 OVERVIEW

20

33

| CHAPTER | 2 CON | ICEPT OF MULTIPLE CPU SYSTEM                                | 26 |

|---------|-------|-------------------------------------------------------------|----|

| 2.1     | CPU   | Numbers.                                                    |    |

| 2.2     | I/O N | lumber Assignment                                           |    |

|         | 2.2.1 | I/O numbers of I/O modules and intelligent function modules |    |

|         | 2.2.2 | I/O numbers of CPU modules                                  |    |

#### CHAPTER 3 SYSTEM CONFIGURATION

| 3.1 | Syste | em Using Basic Model QCPU as CPU No.1                                                            |

|-----|-------|--------------------------------------------------------------------------------------------------|

|     | 3.1.1 | Available CPU modules, base units, power supply modules, and extension cables $\ldots \ldots 34$ |

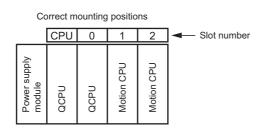

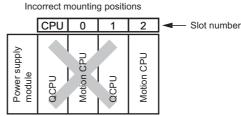

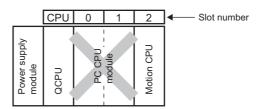

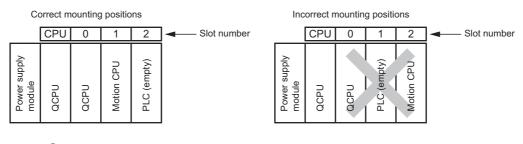

|     | 3.1.2 | CPU module combinations and mounting positions                                                   |

|     | 3.1.3 | Available I/O modules and intelligent function modules                                           |

| 3.2 | Syste | em Using High Performance Model QCPU or Process CPU as CPU No.1                                  |

|     | 3.2.1 | Available CPU modules, base units, power supply modules, and extension cables $\ldots \ldots 43$ |

|     | 3.2.2 | CPU module combinations and mounting positions                                                   |

|     | 3.2.3 | Available I/O modules and intelligent function modules                                           |

| 3.3 | Syste | em Using Universal Model QCPU as CPU No.1                                                        |

|     | 3.3.1 | Available CPU modules, base units, power supply modules, and extension cables $\ldots \ldots 55$ |

|     | 3.3.2 | CPU module combinations and mounting positions                                                   |

|     | 3.3.3 | Available I/O modules and intelligent function modules                                           |

| 3.4 | Appli | cable Software                                                                                   |

| 3.5 | Prec  | autions for System Configuration                                                                 |

#### CHAPTER 4 STARTING UP MULTIPLE CPU SYSTEM

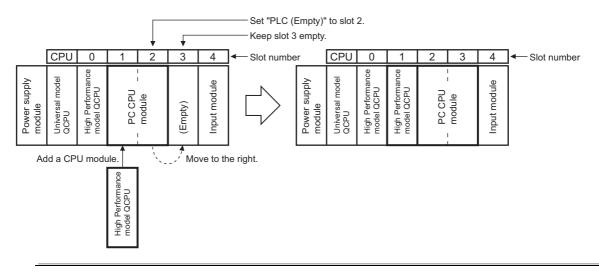

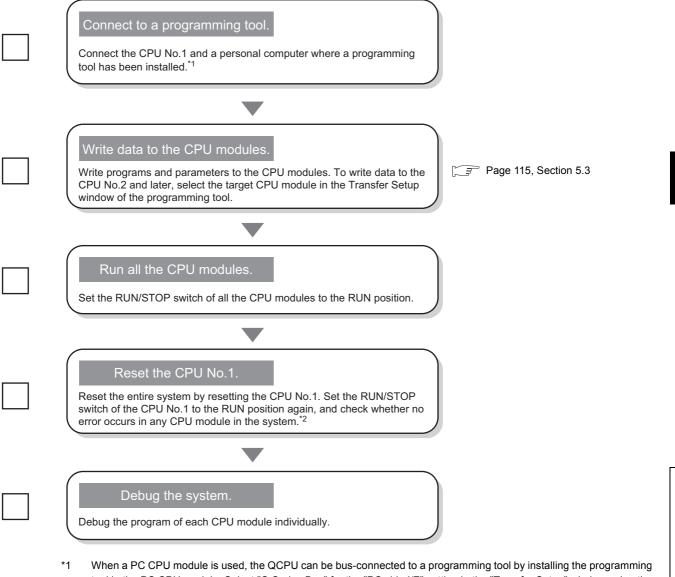

| 4.1 | Proc  | edure Before Operation                                       |

|-----|-------|--------------------------------------------------------------|

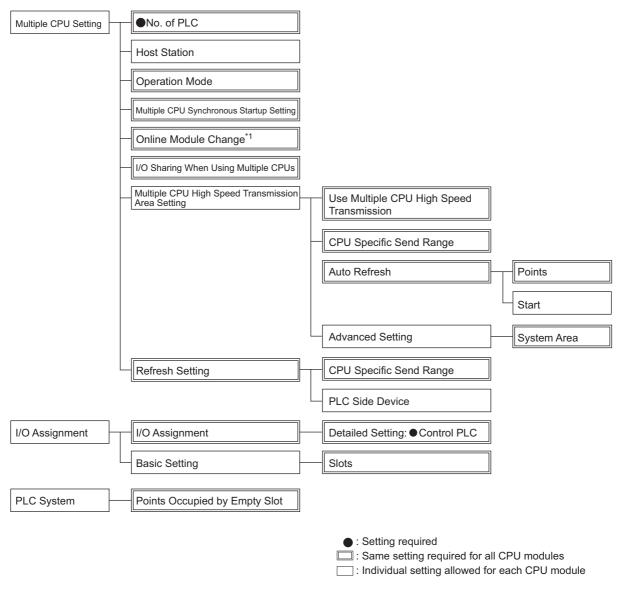

| 4.2 | Oper  | ration Settings                                              |

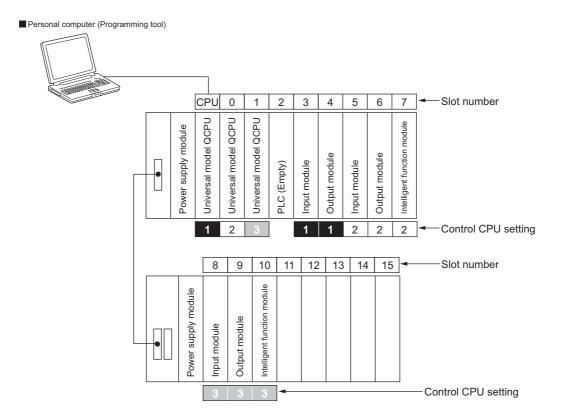

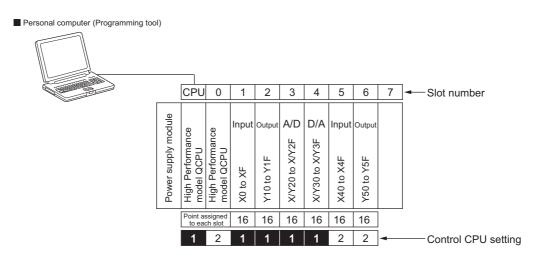

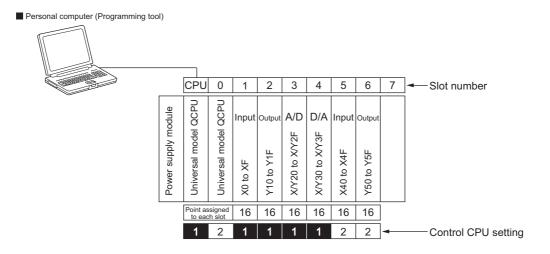

|     | 4.2.1 | System configuration example                                 |

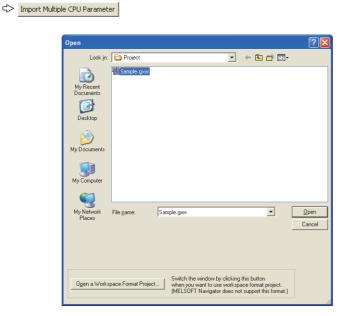

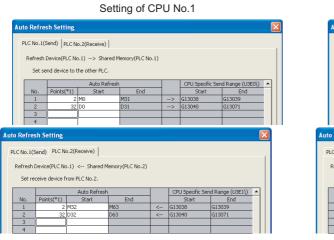

|     | 4.2.2 | Parameter settings                                           |

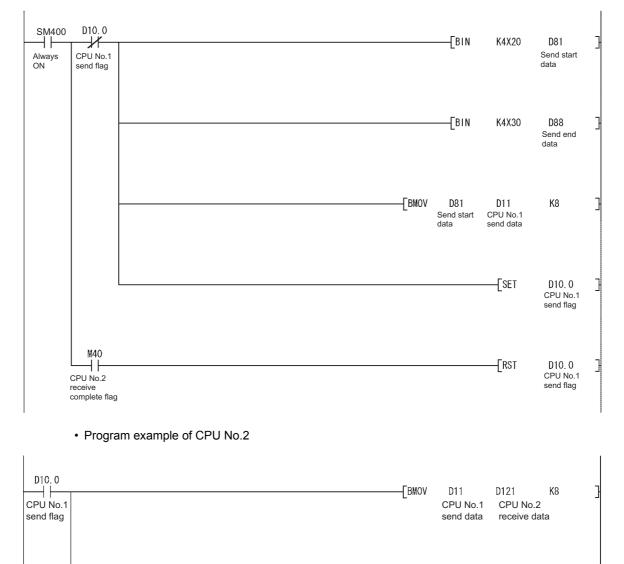

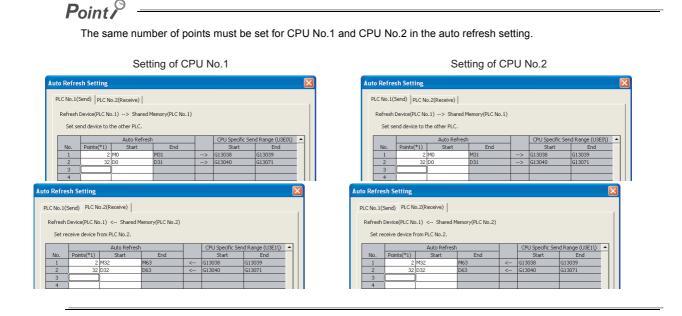

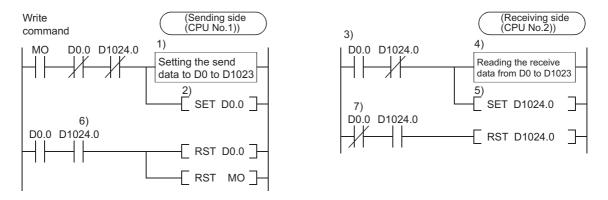

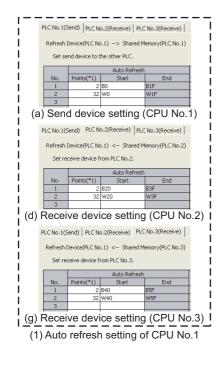

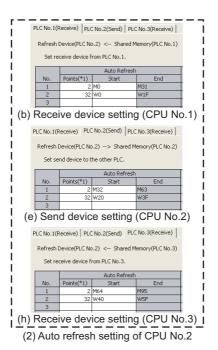

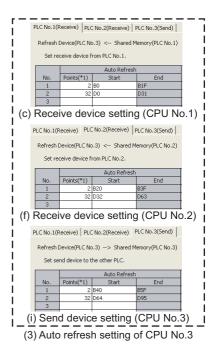

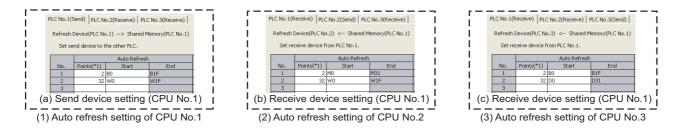

| 4.3 | Prog  | ram Examples for Communications by Auto Refresh              |

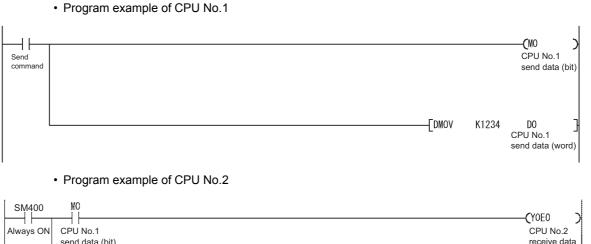

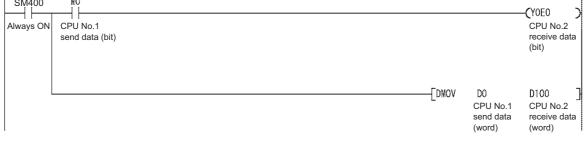

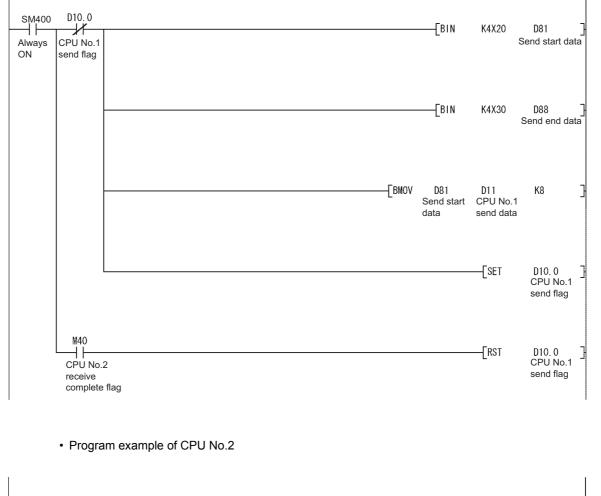

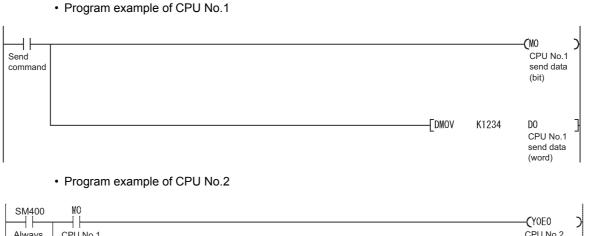

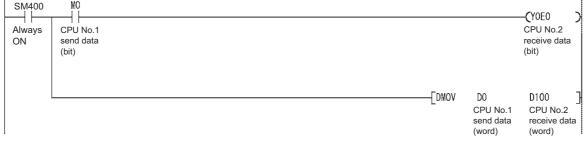

|     | 4.3.1 | Program examples for Basic model QCPU, Qn(H)CPU, and QnPHCPU |

|     | 4.3.2 | Program examples for Universal model QCPU                    |

| 4.4 | Cloc  | k Data                                                       |

|     | 4.4.1 | Clock data of CPU modules                                    |

|     | 4.4.2 | Clock data of intelligent function modules                   |

| 4.5 | Rese  | tting a Multiple CPU System                                  |

| 4.6 | Syste | em Operation When a Stop Error Occurs                        |

| CHAPTER | 5 ACC | CESS BETWEEN CPU MODULES AND OTHER MODULES                | 107 |

|---------|-------|-----------------------------------------------------------|-----|

| 5.1     | Acce  | ess to Controlled Modules                                 | 107 |

| 5.2     | Acce  | ess to Non-controlled Modules                             | 107 |

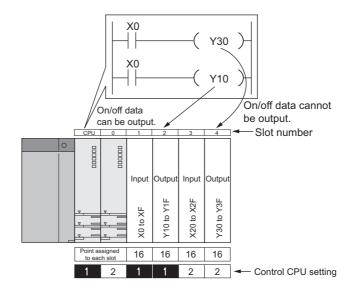

|         | 5.2.1 | Loading input (X) data                                    | 108 |

|         | 5.2.2 | Loading output (Y) data                                   | 110 |

|         | 5.2.3 | Output to output modules and intelligent function modules | 112 |

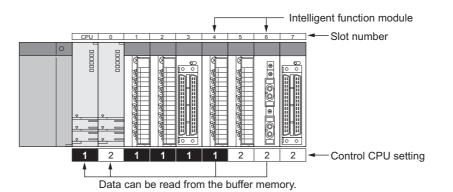

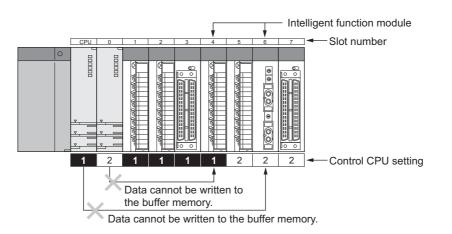

|         | 5.2.4 | Access to the intelligent function module buffer memory   | 113 |

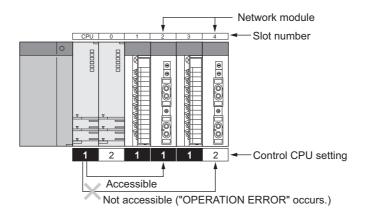

|         | 5.2.5 | Access using the link direct device                       | 114 |

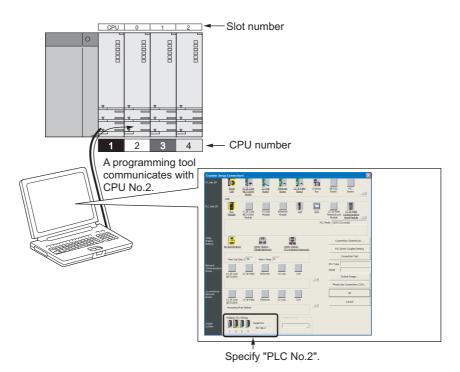

| 5.3     | Acce  | ess From a Programming Tool                               | 115 |

| 5.4     | Acce  | essible QCPUs when GOT is connected                       | 118 |

#### CHAPTER 6 COMMUNICATIONS AMONG CPU MODULES

119

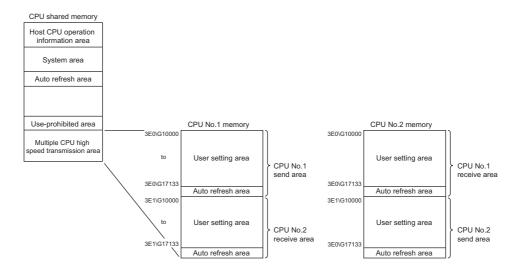

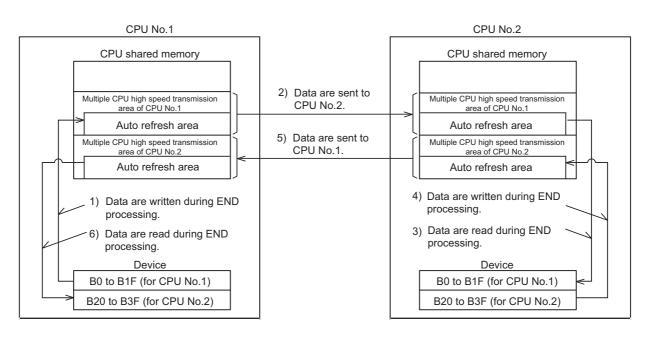

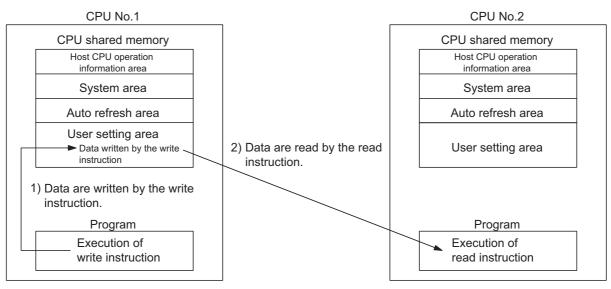

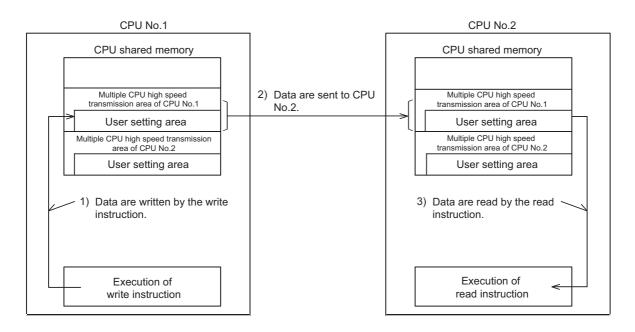

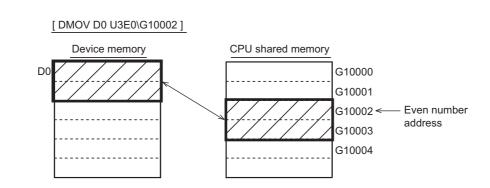

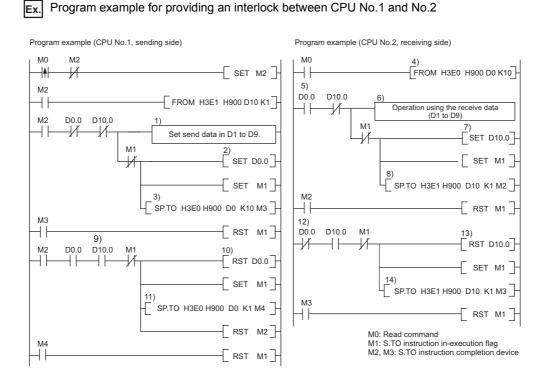

| 6.1 | Com   | munications Using the CPU Shared Memory                                              |

|-----|-------|--------------------------------------------------------------------------------------|

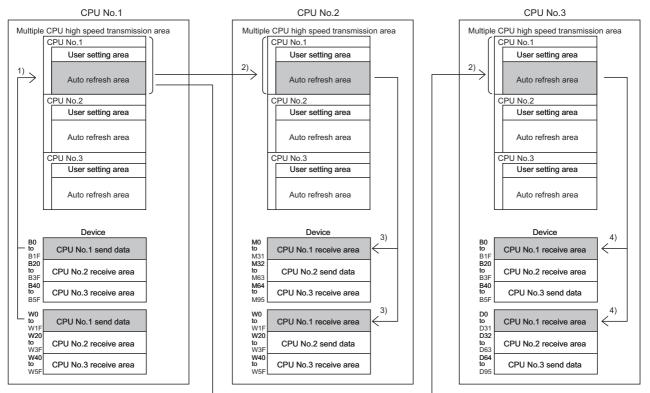

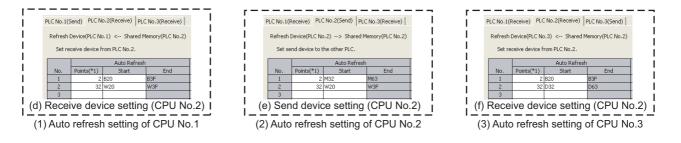

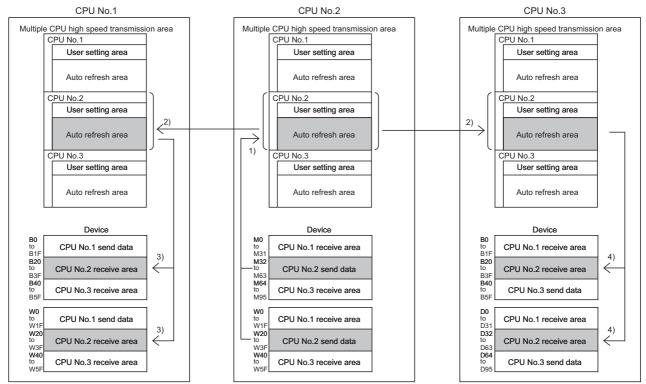

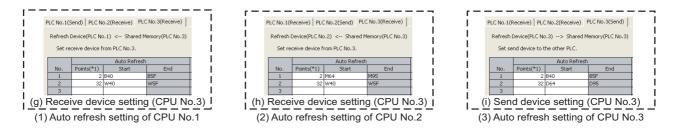

|     | 6.1.1 | Communications by auto refresh (using the auto refresh area)                         |

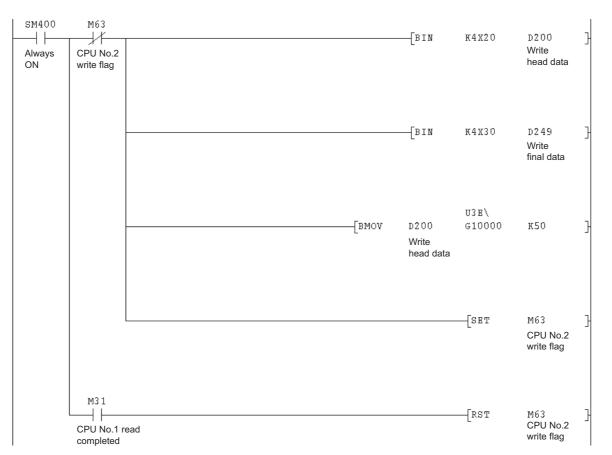

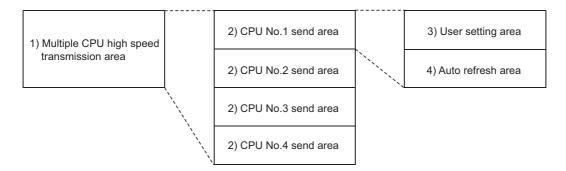

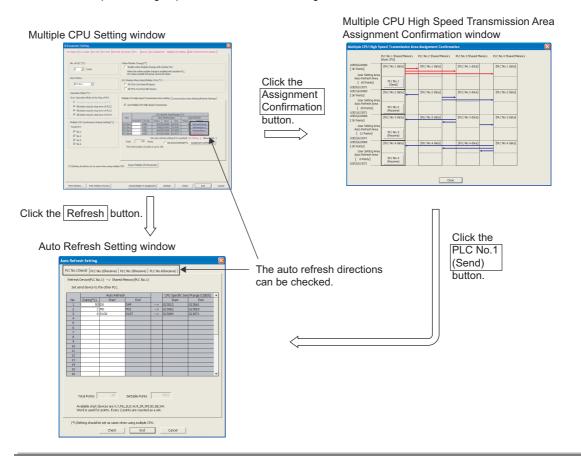

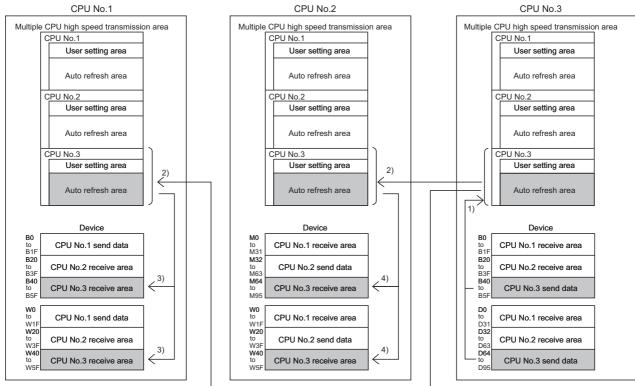

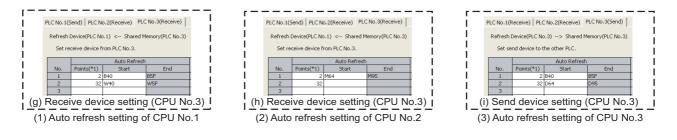

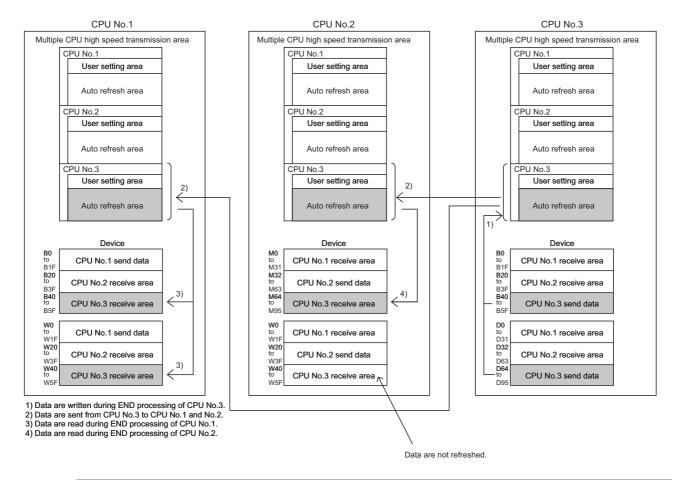

|     | 6.1.2 | Communications by auto refresh (using the multiple CPU high speed transmission area) |

|     |       |                                                                                      |

|     | 6.1.3 | Communications by programs using the CPU shared memory                               |

|     | 6.1.4 | Communications among CPU modules when an error is detected                           |

| 6.2 | Cont  | rol Directions from QCPU to Motion CPU                                               |

| 6.3 | Com   | munications Among CPU Modules By Dedicated Instructions                              |

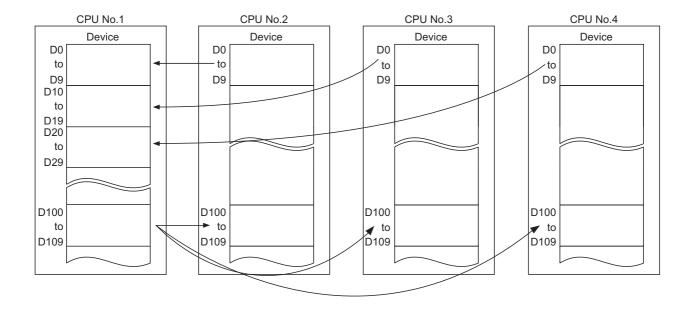

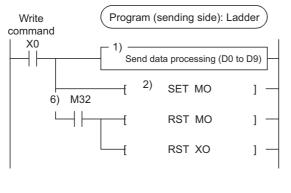

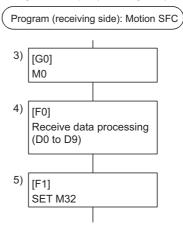

|     | 6.3.1 | Reading/writing device data from/to Motion CPU                                       |

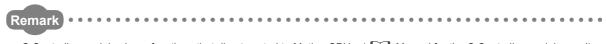

|     | 6.3.2 | Starting interrupt programs                                                          |

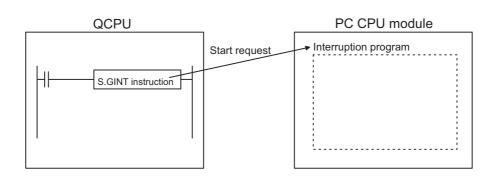

|     | 6.3.3 | Reading/writing device data between QnUCPUs                                          |

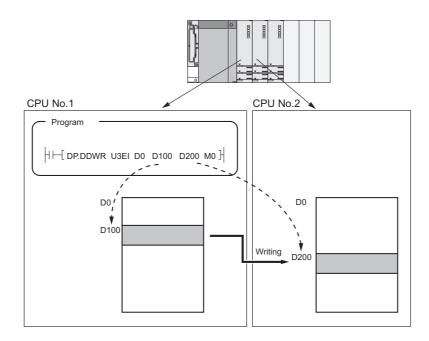

| 6.4 | Multi | ple CPU Synchronous Interrupt                                                        |

| 6.5 | Multi | ple CPU synchronous startup                                                          |

### APPENDICES

| DICES             |                                       | 173 |

|-------------------|---------------------------------------|-----|

| Appendix 1 Param  | eters for a Multiple CPU System       |     |

| Appendix 1.1      | List of parameters                    | 175 |

| Appendix 2 Compa  | arison with a Single CPU System       | 178 |

| Appendix 3 Precau | utions for Using AnS/A Series Modules | 191 |

| Appendix 4 Proces | ssing Time                            | 195 |

| Appendix 4.1      | Concept of scan time                  | 195 |

| Appendix 4.2      | Factors that increase scan time       | 197 |

| Appendix 4.3      | Reducing processing time              | 204 |

| INDEX     | 205 |

|-----------|-----|

| REVISIONS |     |

## MANUALS

To understand the main specifications, functions, and usage of the CPU module, refer to the basic manuals. Read other manuals as well when using a different type of CPU module and its functions. Order each manual as needed, referring to the following lists.

The numbers in the "CPU module" and the respective modules are as follows.

| Number | CPU module                  | Number | CPU module           |

|--------|-----------------------------|--------|----------------------|

| 1)     | Basic model QCPU            | 3)     | Process CPU          |

| 2)     | High Performance model QCPU | 4)     | Universal model QCPU |

•: Basic manual, O: Other CPU module manuals/Use them to utilize functions.

#### (1) CPU module user's manual

| Manual name                                                                                                                    | Description                                                                                                                                                                                               |   | CPU module |    |    |  |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|----|----|--|

| <manual (model="" code)="" number=""></manual>                                                                                 |                                                                                                                                                                                                           |   | 2)         | 3) | 4) |  |

| QCPU User's Manual (Hardware Design,<br>Maintenance and Inspection)                                                            | Specifications of the hardware (CPU modules, power<br>supply modules, base units, extension cables, memory<br>cards, SD memory cards, and extended SRAM<br>cassettes), system maintenance and inspection, | • | •          | •  | •  |  |

| <sh-080483eng (13jr73)=""></sh-080483eng>                                                                                      | troubleshooting, and error codes                                                                                                                                                                          |   |            |    |    |  |

| QnUCPU User's Manual (Function Explanation,<br>Program Fundamentals)<br><sh-080807eng (13jz27)=""></sh-080807eng>              | Functions, methods, and devices for programming                                                                                                                                                           |   |            |    | •  |  |

| Qn(H)/QnPH/QnPRHCPU User's Manual<br>(Function Explanation, Program Fundamentals)<br><sh-080808eng (13jz28)=""></sh-080808eng> | Functions, methods, and devices for programming                                                                                                                                                           | • | •          | •  |    |  |

| QnUCPU User's Manual (Communication via<br>Built-in Ethernet Port)<br><sh-080811eng (13jz29)=""></sh-080811eng>                | Detailed description of communication via the built-in<br>Ethernet ports of the CPU module                                                                                                                |   |            |    | 0  |  |

| QnUDVCPU/LCPU User's Manual (Data<br>Logging Function)<br><sh-080893eng (13jz39)=""></sh-080893eng>                            | Detailed description of the data logging function of the CPU module                                                                                                                                       |   |            |    | 0  |  |

### (2) Programming manual

| Manual name                                                                                                                      | Description                                                                                                     |    | CPU n | nodule | I  |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----|-------|--------|----|

| <manual (model="" code)="" number=""></manual>                                                                                   | Description                                                                                                     | 1) | 2)    | 3)     | 4) |

| MELSEC-Q/L Programming Manual (Common<br>Instruction)<br><sh-080809eng (13jw10)=""></sh-080809eng>                               | Detailed description and usage of instructions used in programs                                                 | •  | •     | •      | •  |

| MELSEC-Q/L/QnA Programming Manual<br>(SFC)<br><sh-080041 (13jf60)=""></sh-080041>                                                | FC)         programming, and error codes for SFC (MELSAP3)                                                      |    |       | 0      | 0  |

| MELSEC-Q/L Programming Manual (MELSAP-<br>L)<br><sh-080076 (13jf61)=""></sh-080076>                                              | System configuration, specifications, functions,<br>programming, and error codes for SFC (MELSAP-L)<br>programs | 0  | 0     | 0      | 0  |

| MELSEC-Q/L Programming Manual (Structured<br>Text)<br><sh-080366e (13jf68)=""></sh-080366e>                                      | System configuration and programming using structured text language                                             | 0  | 0     | 0      | 0  |

| MELSEC-Q/L/QnA Programming Manual (PID<br>Control Instructions)<br><sh-080040 (13jf59)=""></sh-080040>                           | Dedicated instructions for PID control                                                                          | 0  | 0     |        | 0  |

| MELSEC-Q Programming/Structured<br>Programming Manual (Process Control<br>Instructions)<br><sh-080316e (13jf67)=""></sh-080316e> | Dedicated instructions for process control                                                                      |    |       | 0      |    |

### (3) Operating manual

| Manual name                                                                                   | Description                                                                                                                          | Description |    |    | module |  |  |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|----|----|--------|--|--|

| <manual (model="" code)="" number=""></manual>                                                | Description                                                                                                                          | 1)          | 2) | 3) | 4)     |  |  |

| GX Works2 Version 1 Operating Manual<br>(Common)<br><sh-080779eng (13ju63)=""></sh-080779eng> | System configuration, parameter settings, and online<br>operations (common to Simple project and Structured<br>project) of GX Works2 | ٠           | •  | ٠  | •      |  |  |

| GX Developer Version 8 Operating Manual<br><sh-080373e (13ju41)=""></sh-080373e>              | Operating methods of GX Developer, such as<br>programming, printing, monitoring, and debugging                                       | 0           | 0  | 0  | 0      |  |  |

In this manual, pages are organized and the symbols are used as shown below.

The following page illustration is for explanation purpose only, and is different from the actual pages.

| Ex. shows setting or operating examples.       Setting 'Start XV'' enables modification on the start I/O numbers assigned to connected modules.         Image: Shows reference manuals.       For details, refer to the following.         Image: Shows reference manuals.       Point /*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "" is used for window<br>names and items.<br>1. shows operating<br>procedures. | (1) Setting par<br>(a) Operating<br>1. Open t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ng method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TER 7 VARIOUS SETTINGS                                                                                                                                                                                                                                                                                                                                                                                                  |   | <sup>1</sup> The chapter of the current page is shown. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------|

| Image: Section 21 and the two of the words manual of the convected module.       Page 14, Section 21 and Page | operations.*1 [ ] is used for items in the menu bar and                        | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | And there is a second s |                                                                                                                                                                                                                                                                                                                                                                                                                         | h |                                                        |

| Shows reference     manuals.     Point?     Setting to deconsected module User's Manual (Function Explanation, Program Fundamentalis)     Point?     Setting to deconsected module in "Type". Setting a different type results in "SPUNIT LAV ERR."     reference pages.     Point?     Setting to deconsected module in "Type". Setting a different type results in "SPUNIT LAV ERR."     requires attention.     Point?     Setting to deconsected module in "Type". Setting a different type results in "SPUNIT LAV ERR."     requires attention.     Point?     Setting to deconsected module in "Type". Setting a different type results in "SPUNIT LAV ERR."     requires attention.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ex. shows setting or                                                           | Type<br>Mode Name<br>Ponts<br>Saut XY<br>Interview<br>Interview<br>Setting "Start X<br>Exclusion (Start X)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | letter the type of the connected module.     Select the model anne of the connected module.     Select the model anne of the connected module.     Select the model anne of the connected module.     Select the state IO model anne of the connected module.     Set the following                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page 74. Section 7.1.2           Page 74. Section 7.1.3           Page 74. Section 7.1.4           Page 74. Section 7.1.5           Page 74. Section 7.1.6           Page 75. Section 7.1.6           Other 7.1.6           Page 75. Section 7.1.7 |   | The section of the current page is shown.              |

| information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | manuals.                                                                       | Point 2<br>Softhe type of<br>Softhe type of<br>Point 2<br>Point 2 | L CPU Module User's Manual (Function Explanation, Program Fundam<br>the connected module in "Type", Setting a different type results in "SPUNIT LA<br>the trutcon module, he I/O points must also be the same in addition to the I/O a<br>30, Section 4.2.2)<br>igent module is connected, I/O assignment can be omitted by selecting connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | / ERR *                                                                                                                                                                                                                                                                                                                                                                                                                 |   | Remark shows useful                                    |

\*1 The mouse operation example is provided below. (For GX Works2)

|                                                                                                                                                                                                                                                                                                                | MELSOFT Series GX Wo                                                                                                                                                                                                                 | /orks2 (Unset Project) – [[PRG] MAIN]                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                | <u>: P</u> roject <u>E</u> dit <u>F</u> ind/Replace                                                                                                                                                                                  | e <u>C</u> ompile <u>V</u> iew <u>O</u> nline De <u>b</u> ug <u>D</u> iagno: |

| Menu bar                                                                                                                                                                                                                                                                                                       | D 🖻 💾 🚽 🦗 🗅 🗆 🖉                                                                                                                                                                                                                      | 🗠 🗠 📴 🖷 🖙 📮 🖉 🛃 🔜                                                            |

| Ex. ♥ [Online]                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                      | <b>a• 曲</b> , 방뿛놣뿛앍庌,                                                        |

| and then select [Write to PLC].                                                                                                                                                                                                                                                                                | Navigation                                                                                                                                                                                                                           | ₽ ×                                                                          |

| A window selected in the view selection area is displayed.  Ex.  Project window  Project Project Project Project Project Project Window.  Select [Project] from the view selection area to open the Project window. In the Project window, expand [Parameter] and select [PLC Parameter].  View selection area | Project Project Project Project Program Program Device Comment Program Device Comment Device Comment Device Comment Device Comment Device Memory Device Memory Device Memory Device Nitial Value User Library Connection Destination |                                                                              |

|                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                      | Unlabeled                                                                    |

## TERMS

Unless otherwise specified, this manual uses the following generic terms and abbreviations.

\* I indicates a part of the model or version.

| Term                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Series                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Q series                        | The abbreviation for Mitsubishi MELSEC-Q series programmable controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AnS series                      | The abbreviation for compact types of Mitsubishi MELSEC-A series programmable controller                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A series                        | The abbreviation for large types of Mitsubishi MELSEC-A series programmable controlle                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CPU module type                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPU module                      | A generic term for the Basic model QCPU, High Performance model QCPU, Process<br>CPU, Universal model QCPU, Motion CPU, C Controller module, and PC CPU module.<br>The term in this manual does not include the Redundant CPU because it cannot be used<br>in a multiple CPU system.                                                                                                                                                                                                                                                     |

| QCPU                            | A generic term for the Basic model QCPU, High Performance model QCPU, Process CPU, and Universal model QCPU.<br>The term in this manual does not include the Redundant CPU because it cannot be used in a multiple CPU system.                                                                                                                                                                                                                                                                                                           |

| Basic model QCPU                | A generic term for the Q00CPU and Q01CPU.<br>The term in this manual does not include the Q00JCPU because it cannot be used in a<br>multiple CPU system.                                                                                                                                                                                                                                                                                                                                                                                 |

| High Performance model QCPU     | A generic term for the Q02CPU, Q02HCPU, Q06HCPU, Q12HCPU, and Q25HCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Process CPU                     | A generic term for the Q02PHCPU, Q06PHCPU, Q12PHCPU, and Q25PHCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Universal model QCPU            | <ul> <li>A generic term for the Q00UCPU, Q01UCPU, Q02UCPU, Q03UDCPU, Q03UDVCPU,</li> <li>Q03UDECPU, Q04UDHCPU, Q04UDVCPU, Q04UDPVCPU, Q04UDEHCPU,</li> <li>Q06UDHCPU, Q06UDVCPU, Q06UDPVCPU, Q06UDEHCPU, Q10UDHCPU,</li> <li>Q10UDEHCPU, Q13UDHCPU, Q13UDVCPU, Q13UDPVCPU, Q13UDEHCPU,</li> <li>Q20UDHCPU, Q20UDEHCPU, Q26UDHCPU, Q26UDVCPU, Q26UDPVCPU,</li> <li>Q26UDEHCPU, Q50UDEHCPU, and Q100UDEHCPU.</li> <li>The term in this manual does not include the Q00UJCPU because it cannot be used in a multiple CPU system.</li> </ul> |

| Built-in Ethernet port QCPU     | A generic term for the Q03UDVCPU, Q03UDECPU, Q04UDVCPU, Q04UDPVCPU, Q04UDEHCPU, Q06UDVCPU, Q06UDPVCPU, Q06UDEHCPU, Q10UDEHCPU, Q13UDVCPU, Q13UDPVCPU, Q13UDEHCPU, Q20UDEHCPU, Q26UDVCPU, Q26UDPVCPU, Q26UDEHCPU, Q50UDEHCPU, and Q100UDEHCPU                                                                                                                                                                                                                                                                                             |

| High-speed Universal model QCPU | A generic term for the Q03UDVCPU, Q04UDVCPU, Q06UDVCPU, Q13UDVCPU, and Q26UDVCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Universal model Process CPU     | A generic term for the Q04UDPVCPU, Q06UDPVCPU, Q13UDPVCPU, and Q26UDPVCPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

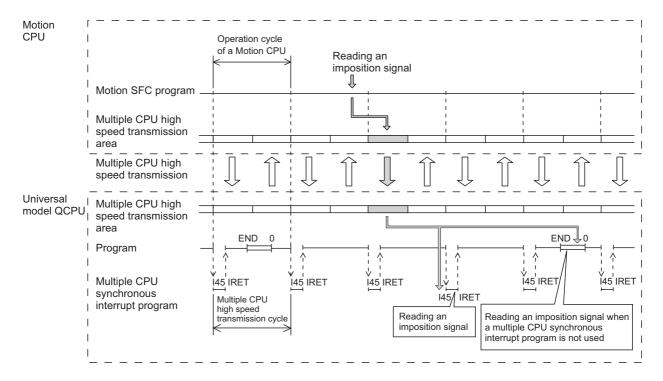

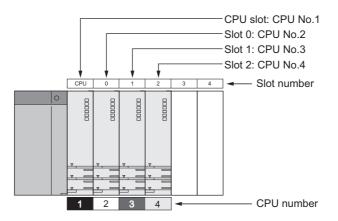

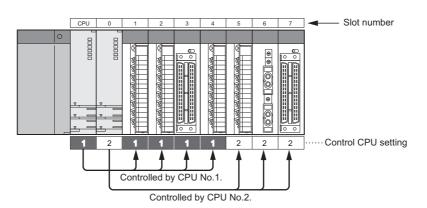

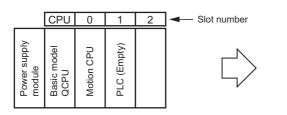

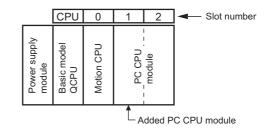

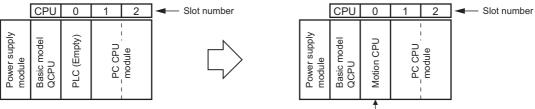

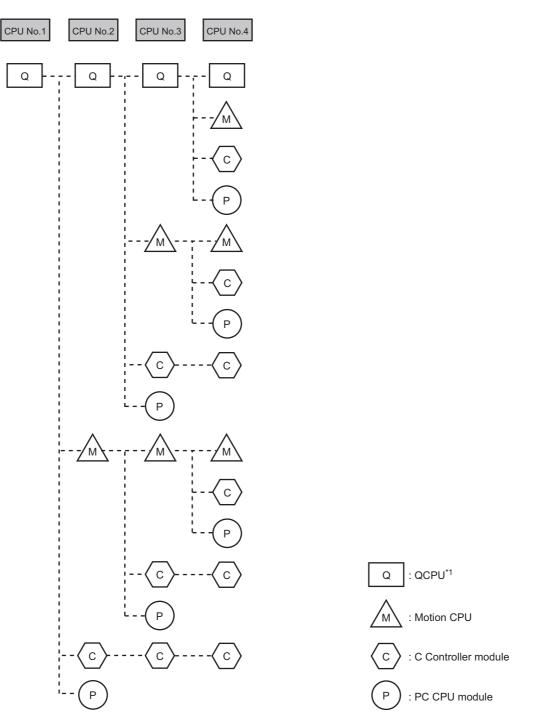

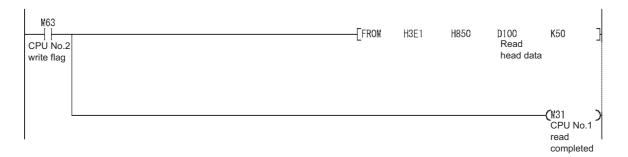

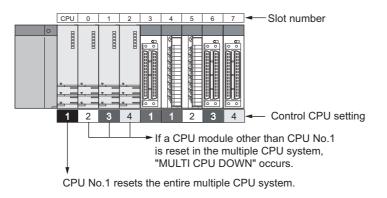

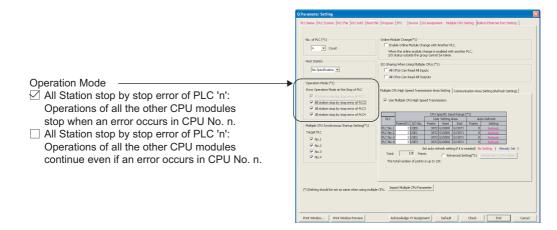

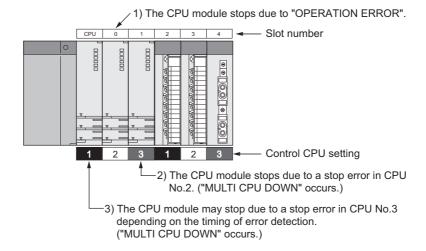

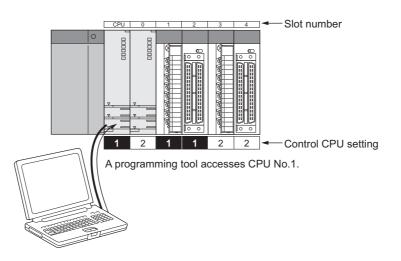

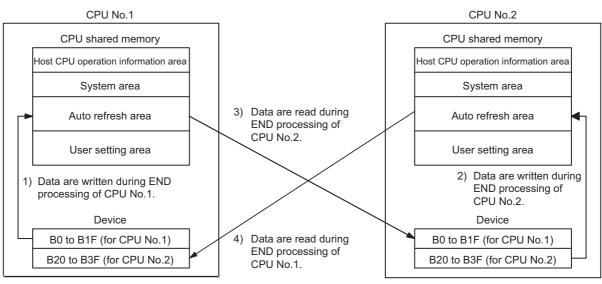

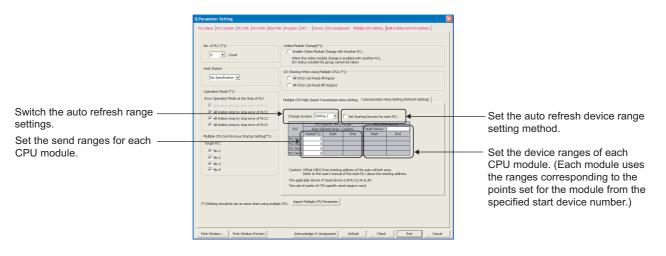

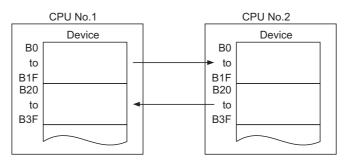

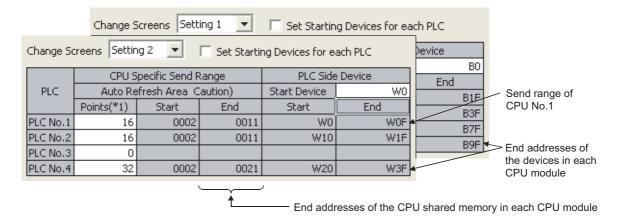

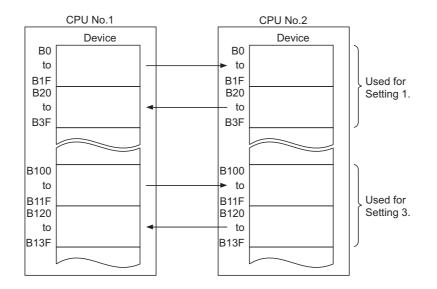

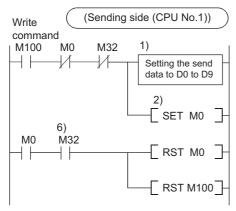

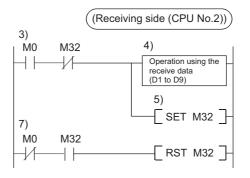

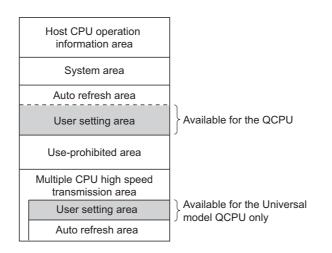

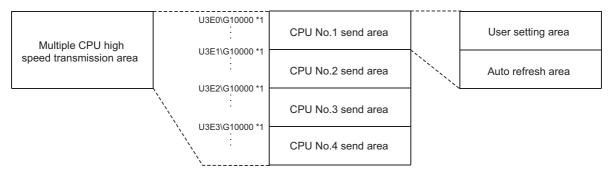

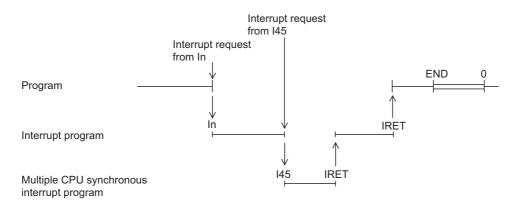

| Motion CPU                      | A generic term for the Mitsubishi motion controllers: Q172CPUN, Q173CPUN, Q172HCPU, Q173HCPU, Q172CPUN-T, Q173CPUN-T, Q172HCPU-T, Q173HCPU-T, Q172DCPU, Q173DCPU, Q172DCPU-S1, Q173DCPU-S1, Q172DSCPU, and Q173DSCPU                                                                                                                                                                                                                                                                                                                     |